Difference between revisions of "Intel Xeon Phi and High Bandwidth Memory"

From crtc.cs.odu.edu

Pthomadakis (talk | contribs) (→Technology) |

Pthomadakis (talk | contribs) (→Technology) |

||

| Line 3: | Line 3: | ||

== Technology == | == Technology == | ||

HBM consists of a number of stacked DRAM dies, with each one having a set of independent channels available to for access by the processors. | HBM consists of a number of stacked DRAM dies, with each one having a set of independent channels available to for access by the processors. | ||

| − | [[File:HBM 9 Comparison.png| | + | [[File:HBM 9 Comparison.png|320px]] |

Revision as of 20:56, 31 May 2018

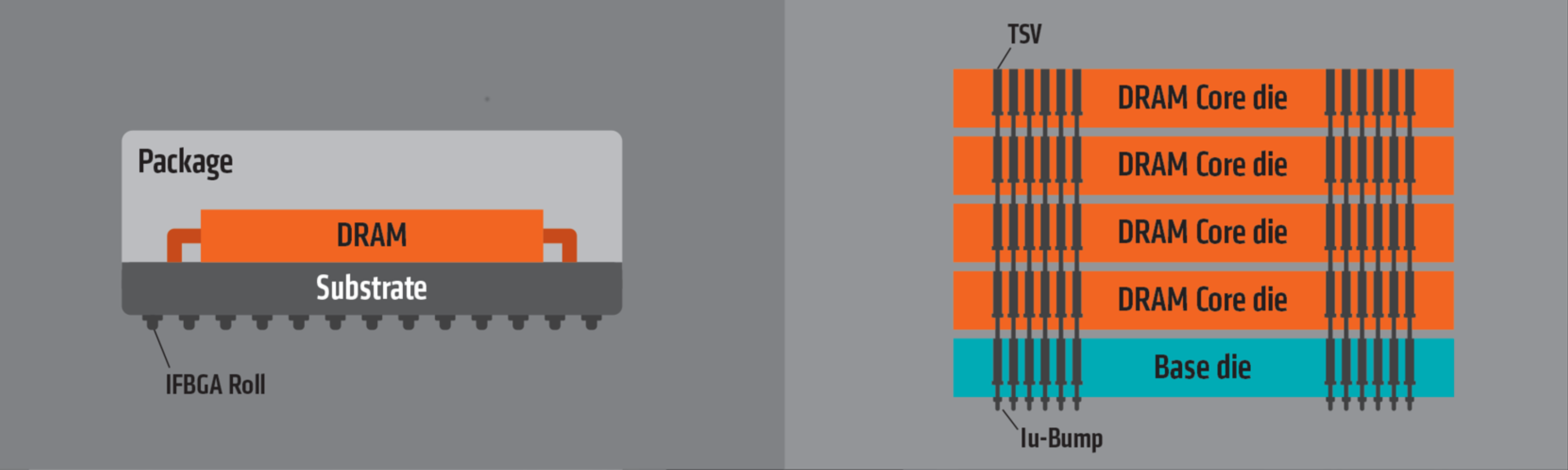

High Bandwidth Memory (HBM) is a high bandwidth RAM interface for 3D-stacked DRAM developed by AMD. Hybrid Memory Cube Interface developed by Micron Technology is also a similar technology but is not compatible with HBM. HBM has been designed to provide higher bandwidth than DDR4 (for CPUs) and GDDR5 (for GPUs) while demanding less power and space. Furthermore, it is compatible with on-chip integration, while other technologies (DRAM, NAND) are not, which allows for even higher performance benefit.

Technology

HBM consists of a number of stacked DRAM dies, with each one having a set of independent channels available to for access by the processors.